总体介绍

PGC1K器件是采用55nm工艺制造的低成本、高密度IO并具有非易失性的产品,采用先进的封装技术,提供上电瞬间启动功能;其中等效LUT4容量为1276 ;包括有专用存储模块(DRM),多样的片上时钟资源,多功能的I/O资源,丰富的布线资源,并集成了SPI,I2C和定时器/计数器等硬核。支持多种配置模式,支持远程升级和双启动功能,同时提供UID(Unique Identification)等功能以保护用户的设计安全。

PGC1K器件包含 G(通用型)、L(低功耗)两种版本,支持两个速度等级-5 和-6,其中-6 为最快等级。G 型器件支持外部供电电压 VCC 为 2.5V或 3.3V,经过内部 LDO 电路产生内核电压,内核电压 VCCCORE是 1.2 V;L型器件只支持 VCC 为 1.2V,VCCCORE与VCC相同。器件的每个 I/O Bank电源由其对应的VCCIO单独供电,支持1.2V、1.5V、1.8V、2.5V 和 3.3V。

主要特征

灵活的架构

- 逻辑资源 1276 个等效 LUT4

- 用户 I/O 29个,3对真差分输出管脚

多功能的I/O

专用存储模块

- 单个 DRM 提供 9Kbits 存储空间

- 支持多种工作模式,包括双口(DP)RAM,简单双口(SDP)RAM,单口(SP)RAM或 ROM 模式,以及 FIFO 模式

- 双口RAM和简单双口RAM支持双端口混合数据位宽

- 支持字节使能功能

支持高速数据传输

- OSERDES 支持 4:1,7:1,8:1

- ISERDES 支持 1:4,1:7,1:8

时钟资源

- 8 条全局时钟线和 8 条全局信号线,支持最高 400MHz

- 4 个 I/O 时钟网络,支持最高 600MHz

- 支持最多 2 个 PLL

多种配置方式及应用

- 支持 JTAG 配置

- 支持主自加载

- 支持主 SPI 配置

- 支持从 SPI 配置

- 支持从 I2C 配置

- 支持从并配置

- 支持双启动功能

- 支持远程升级

- 支持压缩位流

嵌入式硬核

- 2 个 I2C 硬核

- 1 个 SPI 硬核

- 1 个定时器/计数器

- 1 个片上振荡器

应用领域

- 消费类电子产品

- 计算与存储

- 无线通讯

- 工业控制系统

- 自动驾驶系统

资源规模

- CLM LUT5:1064

- CLM 等效LUT4:1276

- CLM FF:1596

- CLM 分布式 ram(Kbits):11

- DRM 9K(每个 DRM 的容量是 9 Kbits):7

- DRM 最大容量(Kbits):63

- PLL:1

- 用户可用的嵌入式Flash最大容量(Kbits):PGC1KL(310Kbits),PGC1KG(80Kbits)

- 硬核 I2C:2

- 硬核 SPI:1

- 硬核 定时器/计数器:1

- 片上振荡器:1

- 是否支持MIPI D-PHY :是

封装与 I/O 数量

-

PGC1KL:

——UWG36(2.5mm * 2.5mm,0.4mm), 29个用户 I/O,3对真差分输出管脚

-

PGC1KG:

—— LPG100(14mm * 14mm,0.5mm), 80个用户 I/O,4对真差分输出管脚

—— LPG144(20mm * 20mm,0.5mm),112个用户 I/O,4对真差分输出管脚

—— MBG256(14mm * 14mm,0.8mm),207个用户 I/O,14对真差分输出管脚

—— FBG256(17mm * 17mm,1.0mm),207个用户 I/O,14对真差分输出管脚

功能说明

可配置逻辑模块(CLM)

CLM(Configurable Logic Module, 可配置逻辑模块)是器件的基本逻辑单元,每个 CLM 包含 4 个 LUT5、6 个寄存器、位扩展功能选择器、快速进位逻辑以及各自独立的 4条级联链,其中级联链包括快速进位链 (Carry Chain),复位/置位控制级联链 (RS Chain),时钟使能控制级联链 (CE Chain)和移位寄存器数据级联链 (SR Chain)。

每个 CLM 中 2 个 LUT5 可以实现 1 个 LUT6,2 个 LUT6 可以实现 1 个 LUT7。相邻的两个 CLM可以实现 1 个 LUT8 逻辑。

CLM 有两种类型:

- CLMA,可实现逻辑、算术、移位寄存器以及 ROM 功能

- CLMS,在 CLMA 实现功能基础上增加分布式 RAM 功能

CLM 可以配置成不同的功能模式:

- 逻辑功能模式

- 算术功能模式

- ROM 存储器模式

- 分布式 RAM 存储器模式

- 多路数据选择器

- 输出寄存器

专用存储模块(DRM)

器件包含 7 个 DRM,每个 DRM 有 9Kbits 存储单元,以及输入寄存器和输出寄存器。

多种工作模式

DRM 支持多种工作模式,包括双口 RAM,简单双口 RAM,单口 RAM 或 ROM 模式,以及 FIFO模式。

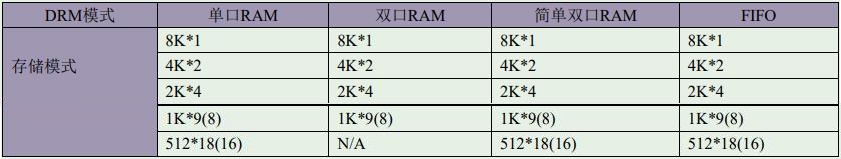

配置列表

支持混合数据位宽

DRM 在双口 RAM 和简单双口 RAM 模式下支持双端口混合数据位宽。

双口 RAM 模式混合数据位宽列表

简单双口 RAM 模式混合数据位宽列表

支持字节使能

DRM 支持写操作的字节使能功能,即通过使能信号实现对选定数据字节的写入,同时屏蔽同一地址索引的其它字节的写入。

可选的输出寄存器

针对数据输出端口,DRM 特别提供了可选的输出寄存器,以取得更好的时序性能。

DRM级联扩展

多个 DRM 可以通过级联扩展的方式组合成更大的双口 RAM,简单双口 RAM,单口 RAM 或 ROM以及 FIFO。对此,DRM 提供额外的 3bits 地址扩展,用于深度扩展的应用。

时钟

器件有最多 8 对专用时钟差分输入管脚,这些管脚可以接收差分输入信号也可以接收单端输入信号。当单端时钟信号接入时,使用差分信号的 P 端。作为时钟输入,这些管脚用来驱动时钟线,当这些管脚不需要驱动时钟线时,也可以作为通用 I/O 使用。

全局时钟网络

全局时钟网络支持 8 个全局时钟以及 8 个全局信号,8 个全局信号也可用作全局时钟使用。

全局时钟可以为器件内的各种资源提供时钟,如 CLM,DRM 和 IO Logic。全局时钟支持 400MHz的时钟频率。全局时钟支持时钟动态使能和动态切换功能。

全局信号用来作为全局控制信号,如时钟使能信号,同步/异步清零、复位或者输出使能信号。

I/O时钟网络

I/O时钟网络有4个,BANK0和BANK2附近各有2个。时钟信号可以通过I/O时钟到达IO Logic,作为信号的高速采样时钟。

I/O 时钟具有频率高(600MHz)和频偏小的特点。I/O 时钟支持动态使能的功能。

PLL

器件最多有 2 个 PLL。PLL 是 CPLD 提供时钟资源的核心子系统,主要功能有时钟频率综合,降低时钟偏移,调整时钟相位以及低功耗管理等。

PLL 的输入时钟支持从外部 I/O 输入和内部互联输入时钟。支持两个输入时钟进行动态切换。PLL的反馈时钟支持从外部 I/O 输入和内部互联输入。

PLL 支持多个时钟输出,每个时钟输出具有独立的分频器,支持 1-128 分频;每个时钟输出可以级联,PLL 之间也可以级联;每个时钟输出具有可选的动态时钟使能控制;PLL 还支持精度为 16 位的小数分频时钟输出,可以让用户产生非整数的输出时钟。

PLL 支持静态配置和动态控制时钟相位两种方式。其中,动态调节 PLL 的相位时,可以用 APB接口改写,或者通过端口来控制。PLL 可以动态连续实现相位逐渐递增或者递减,且相位调节过程中,被调节的时钟输出没有毛刺。

PLL 支持待机(Standby)模式,即在设计中不需要用到 PLL 时,可以让 PLL 处于下电状态,以节省功耗。

PLL 支持用户通过 APB 接口对 PLL 工作参数进行动态地改变,为用户动态配置 PLL 提供另一种方式。详

I/O 单元

IO Buffer(IOB)

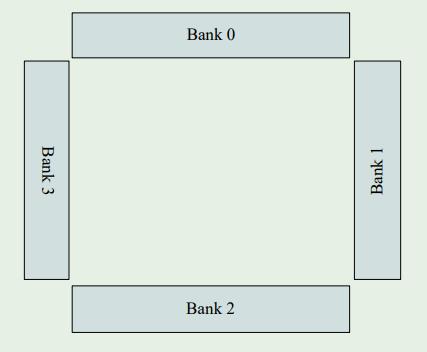

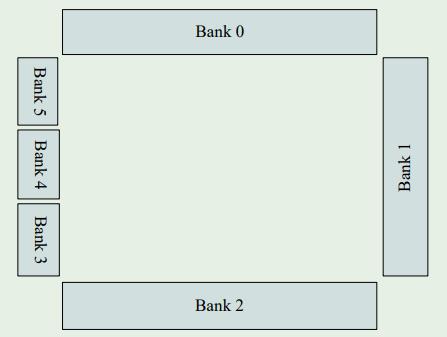

IO Buffer 按照不同器件规模有不同数量的 I/O Bank,各器件的 bank 分布如下图所示。

PGC1KL bank 分布顶视图

PGC1KG bank 分布顶视图

器件 Bank 资源分布

-

UWG 封装的器件只引出 3 个 bank 的 I/O

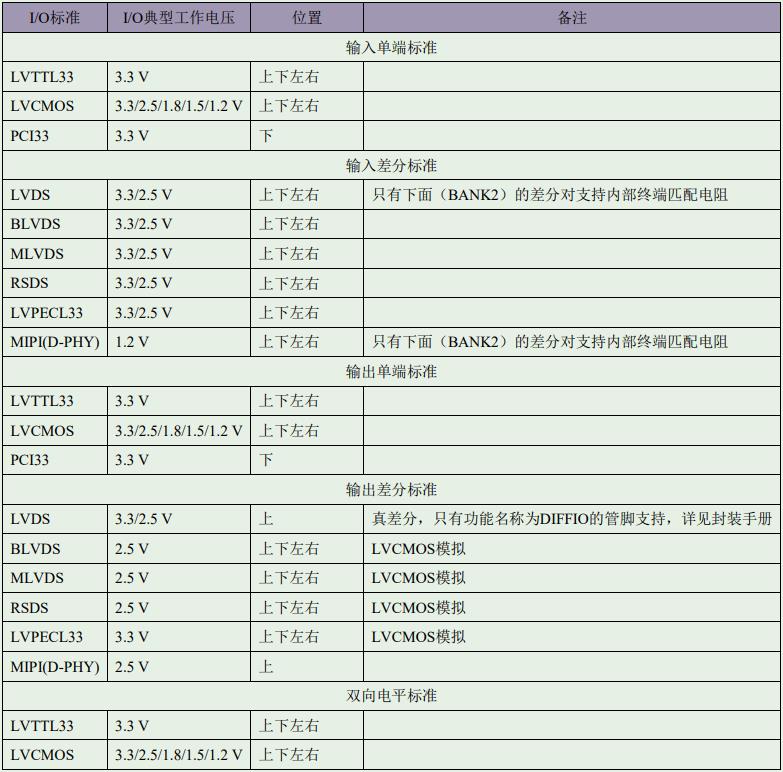

每个 bank 独立支持 1.2V-3.3V bank 电压,整个 bank 中的 IO 不使用时,bank 电源可以悬空或连接正常的工作电压,建议接 VCC。每个 bank 支持多种单端和差分接口标准,以适应不同的应用场景。IO Buffer 功能强大,可灵活配置 I/O 标准、输出驱动能力、摆率、输入迟滞和总线保持状态等。此外,IO Buffer 还支持热插拔属性,防止芯片由于泄漏电流过大而损坏;支持内部差分输入终端匹配电阻100Ω,支持 LVDS 和 MIPI 电平标准。

器件的所有 I/O 都支持差分输入,但只有器件下侧(Bank2)的 I/O 支持内部差分输入终端匹配电阻。上侧(Bank0)的部分 I/O 支持真差分输出(定义为 DIFFIO 的管脚支持真差分输出)。

支持的 I/O 标准

IO Logic(IOL)

IO Logic 主要包含以下功能:

- 输入、输出、三态组合逻辑

- 输入寄存器(触发器/锁存器),输出寄存器(触发器)和三态寄存器(触发器)

- IDDR(1:2)和ODDR(2:1),其中ODDR包括输出和三态的ODDR

I/O 输入输出延迟单元

I/O 输入延迟功能和输出延迟功能分别由同一个延迟单元单独实现。所有 I/O 均支持输入和输出延迟的静态配置,但只有器件下侧的 I/O 支持动态可调输入延迟,所有 I/O 都不支持动态可调输出延迟。

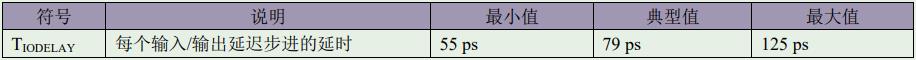

I/O 延迟单元的步进延时

高速数据传输

I/O 单元通过与 ISERDES 和 OSERDES 模块配合使用,可以实现高速数据的收发。

-

ISERDES:针对高速接口,支持1:4,1:7,1:8

-

OSERDES:针对高速接口,支持4:1,7:1,8:1

所有 Bank 都支持 IDDR/ODDR 和输入/输出/三态寄存器。针对高速接口应用,下侧的 Bank 支持ISERDES,上侧的 Bank 支持 OSERDES。

热插拔

器件支持 2 级热插拔功能。每个 IO Buffer 都支持热插拔功能,以防止当器件供电电压低于外部输入信号电压时,电流从信号管脚流入器件衬底,导致 latch-up 产生。

片上振荡器

器件都有一个片上振荡器(OSC)。OSC 的输出可以通过编程互联到全局时钟网络或者互联到 PLL 作为 PLL 的参考时钟。OSC 的输出还可以为配置系统提供可编程配置时钟,作为主配置时钟使用。OSC 的输出也可以为嵌入式 Flash 提供固定频率时钟。

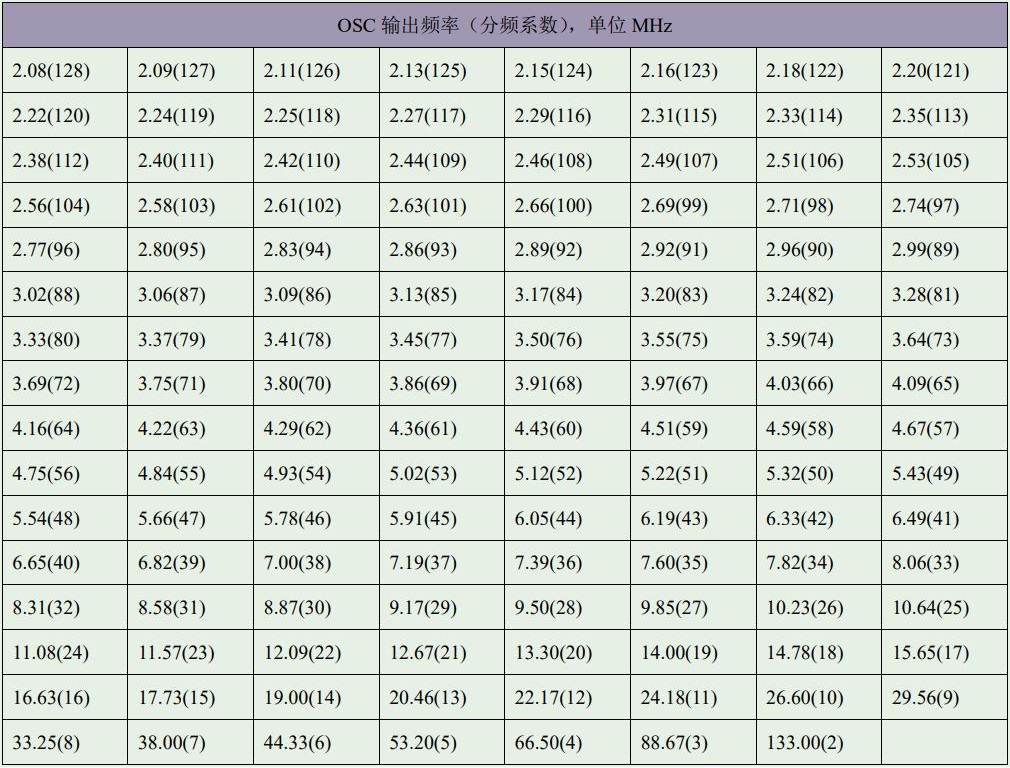

用户可通过例化 GTP_OSC_E2 进行 OSC 的时钟分频。OSC 的本征频率为 266MHz,整数分频系数范围为 2-128,OSC 输出频率范围为 2.08MHz-133MHz,这些频点是非连续的,默认值为 2.08MHz。当 OSC 输出的时钟作为用户时钟时,可输出的频率如下所示。

OSC 输出频率

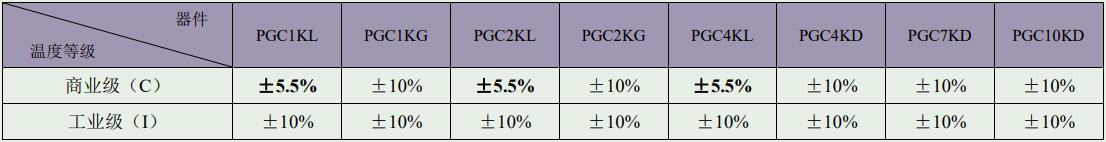

器件的 OSC 精度列表

嵌入式硬核

器件内嵌了多个硬核,如 I2C、SPI 和定时器/计数器。用户可通过 APB 接口访问这些硬核。

I2C 硬核

器件都包含 2 个 I2C 硬核,每个 I2C 硬核都可以配置为主设备和从设备。当 I2C 硬核被配置为主设备时,它就可以通过 I2C 总线接口控制其他设备;当它做为从设备时,它可以为 I2C 主设备提供扩展 I/O。

I2C 硬核主要支持如下功能:

-

可配置为主设备或从设备,支持主从操作

-

7-bit 和 10-bit 寻址

-

多个主设备仲裁

-

支持快速模式/标准模式 I2C 总线协议,最高 400kHz 的数据传输速度

-

8-bit APB 总线的用户接口

-

支持软复位

-

支持中断

-

支持全呼地址

SPI 硬核

器件都包含 1 个 SPI 硬核,它可以配置为主设备或从设备。当它做为主设备时,它可以通过 SPI 总线去控制其他带有 SPI 接口的芯片;当它做为从设备时,它可以当做外部 SPI 主设备的接口。SPI 硬核支持如下功能:

-

可配置为主设备或从设备,支持主从操作

-

支持中断

-

双缓冲数据寄存器

-

极性和相位可编程的串行时钟

-

数据传输支持最低位先发或最高位先发

-

8-bit APB 总线的用户接口

-

最多控制 8 个从设备

定时器/计数器硬核

器件都提供了一个通用的,双向 16-bit 的定时器/计数器硬核。它有独立的输出比较单元并支持脉宽调制。该硬核支持如下功能

-

支持如下工作模式

——看门狗

——自动清零定时器

——快速脉宽调制

——相位和频率校正脉宽调制

-

可编程的时钟输入

-

支持中断请求

-

自动重加载

-

支持时间戳

-

8-bit APB 总线的用户接口

嵌入式 Flash

器件包含了一个嵌入式 Flash,它可以用来存储配置信息,或者为用户提供通用的 Flash 存储空间。嵌入式 Flash 有如下特点:

- 供电电压 1.2V,由 VCCCORE 提供

- 存储空间为 80 Kbits和310Kbits

- 至少 10 万次擦写操作

- 自加寻址

- 支持 JTAG,I2C,SPI 和 APB 接口

上电复位电路(POR)

器件具有上电复位电路(POR),它在器件上电时和工作期间监控器件的VCCCORE 和 VCCIO0。上电开始后,当 POR 电路检测到 VCCCORE和 VCCIO0 达到 VPUP(如表 16 所示)后,器件就会开始进行初始化。

复用 I/O 可通过设置特征控制位来设置成配置 I/O 或用户 I/O。所有 I/O 在上电期间为低电平;在配置前和配置期间,用户 I/O 呈弱下拉,配置 I/O 呈弱上拉或其固有状态;在配置完成进入用户模式后,用户 I/O 才释放给用户使用。

进入用户模式后,POR 电路继续监控 VCCCORE。如果 VCCCORE 降到 VPDN 指定的电压,芯片不能保证正确工作;一旦发生这种情况,POR 电路复位整个芯片,并再次监控 VCCCORE 和 VCCIO0。

配置与测试

配置

器件包含多种配置接口,JTAG、SPI 和 I2C。其中, JTAG 支持 IEEE 1149.1边界扫描规范和 IEEE 1532 系统内配置规范。在这些配置接口的支持下,可以有多种模式来配置器件。

-

主自加载

-

JTAG 模式

-

主 SPI 模式

-

从 SPI 模式

-

从 I2C 模式

-

从并模式

器件上电完成后,开始进行器件的初始化操作,然后选择配置模式;不同的配置模式有不同的配置接口,配置模式确定后,对应的管脚就被设置为配置管脚,然后进行位流的加载;完成位流的加载后,进行 CRC 校验;CRC 校验成功后,进入用户模式。

所有的配置管脚都是复用的,当一些配置管脚没有被用来做配置功能时进入用户模式后,它们就可以用来做通用 I/O。

器件支持压缩位流。

器件支持回读功能,用来从 CRAM 里读出配置数据。在回读的过程中并不影响系统的正常工作。同时也支持禁止回读,保护用户信息安全。

器件支持双启动功能。

器件支持远程升级功能。

边界扫描测试

器件集成了边界扫描单元,它支持 IEEE 1149.1,用户可以通过 JTAG 进行访问。JTAG 包含 4 个信号,TDI,TDO,TCK 和 TMS。

器件内部的每个 I/O 都附加了一个边界扫描单元,这些边界扫描单元在器件内部通过输入输出管脚相互串联起来。测试数据从 TDI 端口进入,通过串行移位的方式访问每个 I/O,然后从 TDO 流出,通过分析测试响应,可以实现待测电路的故障诊断。

JTAG 的端口由 VCCIO0 供电,支持 LVCMOS33/ LVCMOS25/ LVCMOS18/ LVCMOS15/LVCMOS12。

UID(Unique Identification)

每个器件都有唯一的 UID,它可以用来跟踪信息或者保证 IP 的安全性。UID 的位宽是 64 位,只读不可写。UID 可以通过片内 UID 接口或者片内 APB 接口进行读操作,也可以通过 SPI,I2C 或者 JTAG 接口进行读操作。